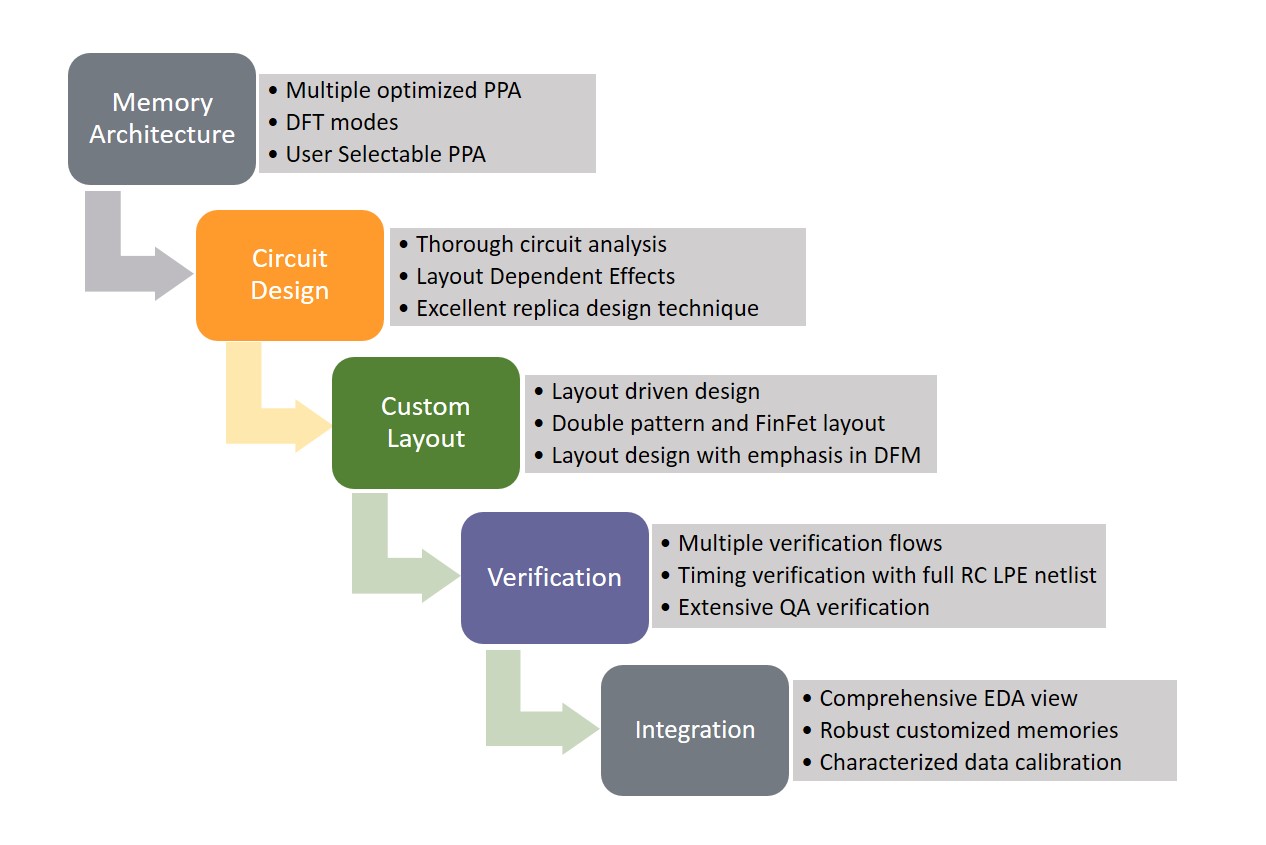

Memory Compiler

- Multiple PPA optimized points

- Comprehensive DFT modes

- User Selectable PPA Optimization Methodology

- Thorough circuit analysis with Monte Carlo Simulation

- Layout Dependent Effects are carefully analyzed in critical circuits

- Excellent replica design technique

- Layout driven design approach to optimize PPA

- Experience in double pattern and FinFet layout

- Layout design with emphasis in DFM

- Multiple verification flows with same source of data

- Timing verification with full RC LPE netlist

- Extensive QA verification

- Comprehensive EDA views

- Robust customized memories with silicon proven quality

- Comprehensive characterization data with memory compiler test chip

Savarti designers, experts in all aspects of embedded memory compilers, starting from memory architectures, circuit to layout customization, verification, physical design to product tape-out. Our teams are here to offer significant design and efficient development in the most advanced available technologies.

Our expertise in Memory Compiler includes:

- Innovative and second-to-none compiler with massive libraries

- Allowing customization in performance, power and areas

- Proven track records on memory design, customization and production

Our propriety User Selectable PPA Optimization Memory Compilers consists a rich set of fully optimized SRAM based memory compilers. Our offerings include both standard memory compilers and specialty memory compilers in most-advanced technologies.

Standard memory compilers:

- Single port SRAM

- Dual port SRAM

- 2-port Register File

- 1-port Register File

Specialty memory compilers:

- TCAM

- CAMRAM

- Pseudo 2-port SRAM

- Pseudo dual port SRAM